How to Characterize and Test DDR5 Receiver Compliance

Setting up a DDR5 receiver compliance test

Ensuring compliance of the fifth generation of double data rate memory (DDR5) devices requires performance of an exhaustive list of interoperability tests set forth the JEDEC specifications. Physical layer receiver conformance testing involves characterization of the receiver, calibration of a stress signal using a high-bandwidth oscilloscope, and device receiver tests using a bit error ratio tester.

Calibrating the test setup requires precise instruments and is prone to user error, especially without expertise in the nuances of the latest DDR5 compliance test specifications. Manually performing each bit error ratio measurement on the DDR5 DRAM or other device with the calibrated stress signal, recording the results, and comparing them with the test specification is time-consuming. Automated DDR5 receiver test compliance software is required.

DDR5 receiver compliance test solution

See demo of DDR5 receiver test

Explore products for DDR5 receiver test solution

-

![M8040A 64 GBaud High-Performance BERT]()

M8040A 64 GBaud High-Performance BERT

-

![UXR0254A Infiniium UXR-Series Oscilloscope: 25 GHz, 4 Channels]()

UXR0254A Infiniium UXR-Series Oscilloscope: 25 GHz, 4 Channels

-

![D9020JITA Jitter, Vertical, and Phase Noise Analysis Software for Infiniium 90000, V-, Z-, and UXR-Series Oscilloscopes]()

D9020JITA Jitter, Vertical, and Phase Noise Analysis Software for Infiniium 90000, V-, Z-, and UXR-Series Oscilloscopes

-

![D9020ASIA Advanced Signal Integrity Software (Crosstalk)]()

D9020ASIA Advanced Signal Integrity Software (Crosstalk)

-

![M80885RCA DDR5 Receiver Conformance and Characterization Test Application]()

M80885RCA DDR5 Receiver Conformance and Characterization Test Application

How to Characterize and Test DDR5 Receiver Compliance

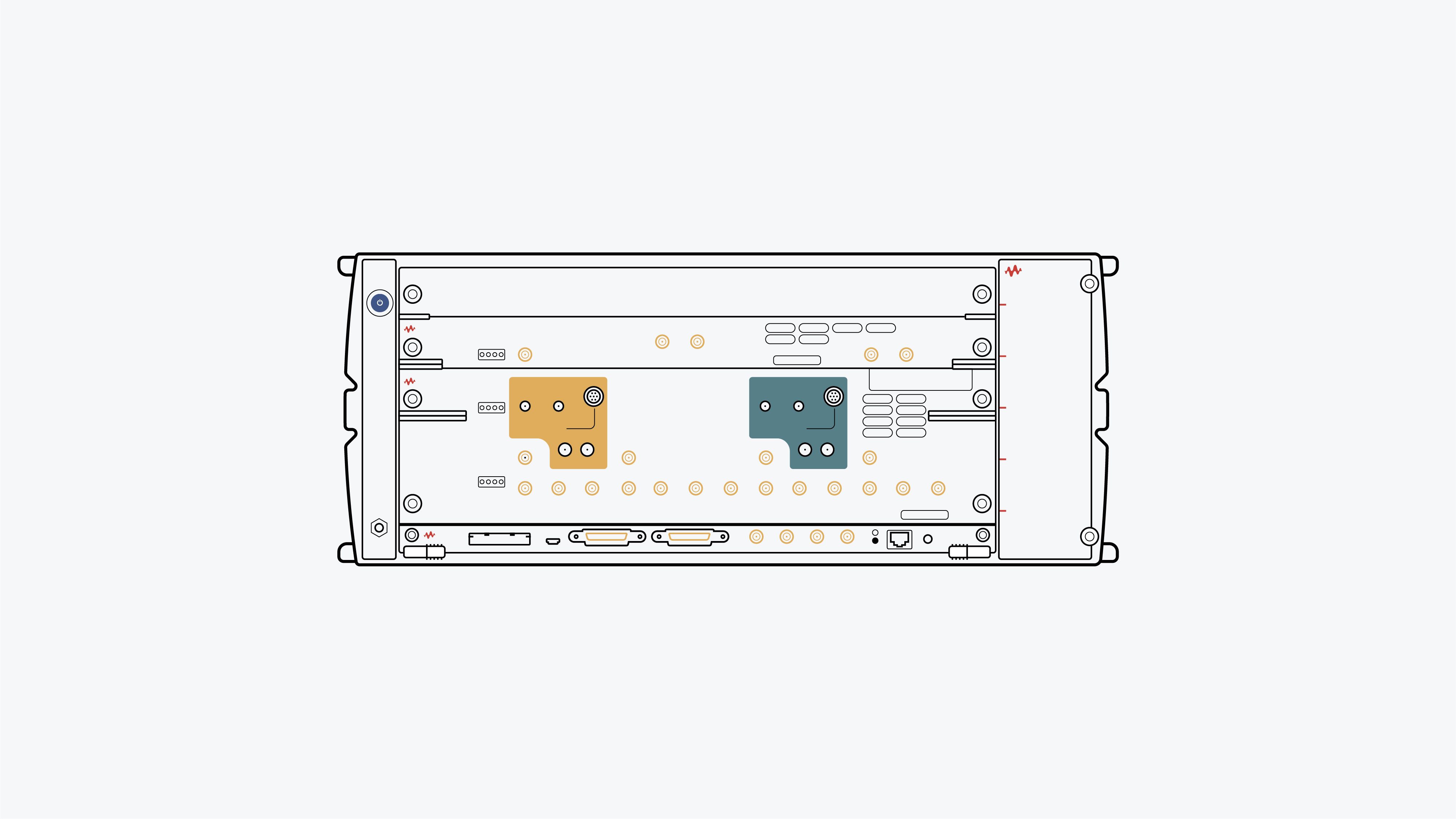

M8040A 64 GBaud High-Performance BERT

The M8040A high performance BERT covers all flavors of 400 GbE standards testing with support for PAM4 and NRZ signals and data rates up to 64 GBaud

Specs

| Standards |

|

| Module Type |

|

| Amplitude | 0.9 Vpp @ 58 GBd |

| Clock data recovery built-in | Yes w/ adj loop bandwidth (16 MHz max) |

| Equalizer |

|

| FEC |

|

| Jitter Type |

|

| Line Coding |

|

| Link Training |

|

| Number of channels |

|

| Type |

|

| Supported Data Rates | 64 Gbaud |

| Max sample rate | 64.8 GBd |

How to Characterize and Test DDR5 Receiver Compliance

UXR0254A Infiniium UXR-Series Oscilloscope: 25 GHz, 4 Channels

The UXR0254A is the 25 GHz, 4 channel, Infiniium UXR-Series real-time oscilloscope.

Specs

| Bandwidth | 25 GHz |

| Max memory depth | 2 Gpts |

| Max sample rate | 128 GSa/s |

| Type |

|

How to Characterize and Test DDR5 Receiver Compliance

D9020JITA Jitter, Vertical, and Phase Noise Analysis Software for Infiniium 90000, V-, Z-, and UXR-Series Oscilloscopes

EZJIT Software for 90000/V-/Z-/UXR-Series Oscilloscopes

Specs

| Debug & Analysis Software |

|

| Connectivity & Usability Software |

|

| Compliance Test Applications |

|

| Select Oscilloscope Series |

|

| Software Type | |

| Applications |

|

| Compatible Instruments |

How to Characterize and Test DDR5 Receiver Compliance

D9020ASIA Advanced Signal Integrity Software (Crosstalk)

Advanced Signal Integrity Software (EQ, InfiniiSimAdv, Crosstalk)

Specs

| Debug & Analysis Software | |

| Connectivity & Usability Software |

|

| Compliance Test Applications |

|

| Select Oscilloscope Series |

|

| Software Type | |

| Applications |

|

| Compatible Instruments |

How to Characterize and Test DDR5 Receiver Compliance

M80885RCA DDR5 Receiver Conformance and Characterization Test Application

M80885RCA receiver conformance and characterization test automation software for DDR5 plus test setup calibration procedures

Specs

| License Types |

|

| Standards |

|

| Test Types | Conformance / Compliance Test |

| Compatible Instruments |

|

Discover resources and insights

Additional resources for DDR5 receiver test

-

Datasheet

Read the DDR5 receiver conformance and characterization software datasheet

-

White paper

Learn how DDR5 increases data center speeds

-

Datasheet

Read about the W5643A DDR5 78-ball BGA interposer

-

White paper

Learn how DDR technology progressed from DDR3 to DDR5

Related use cases

-

![How to Test USB4 Receiver Compliance]() segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers

segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testerssegmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:business-unit/CSG,keysight:product-lines/1a,segmentation:funnel/mofu,segmentation:search-relevance-product/software,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testersHow to Test USB4 Receiver Compliance

Testing physical layer (PHY) USB4 electrical performance requires executing conformance tests defined by the Universal Serial Bus Implementers Forum (USB-IF). Learn how to tune and calibrate a bit error ratio tester's (BERT) stress signal amplitude, channel equalization, and insertion loss to achieve accurate stress conditions required for conformance testing.

Learn more

-

![How to Test USB4 Version 2.0 Receiver Compliance]() segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTs

segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTssegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Oscilloscopes_BERTs_AWGs,keysight:product-lines/1a,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,segmentation:product-category/Oscilloscopes_BERTs_AWGs/BERTsHow to Test USB4 Version 2.0 Receiver Compliance

USB4 Version 2.0 receiver testing requires precise stress signal calibration, consistently repeatable pattern generation, and bit error rate measurements. Learn how to perform a USB4 Version 2.0 receiver compliance test using a bit error ratio tester (BERT), a high-bandwidth oscilloscope, USB receiver test application software, and the USB-IF SigTest utility.

Learn more

-

![How to Test PCIe® 6.0 Receiver Compliance]() segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/software

segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwareHow to Test PCIe® 6.0 Receiver Compliance

Testing PCI-SIG devices requires robust receiver compliance validation to certify PCIe® 6.0 device interoperability at 64 GT/s with PAM4 signals. Learn how to calibrate your stress signal and test for PCIe 5.0 receiver compliance with automated test tools.

Learn more

Get in touch with one of our experts

Need help finding the right solution for you?