What are you looking for?

DDR and LPDDR Memory

Next-generation AI presents various challenges for memory technology. Training AI models requires extremely high-bandwidth memory; low memory latency is needed for inference applications. Large and scalable memory capacity is a must to address growing model sizes.

Keysight has you covered with high-precision and ultra-fast solutions for every stage of your next double data rate 5 (DDR5) and low-power double data rate 6 (LPDDR6) design — for data centers, consumer electronics, automobiles, and other memory systems.

DDR Design-to-Test Solutions

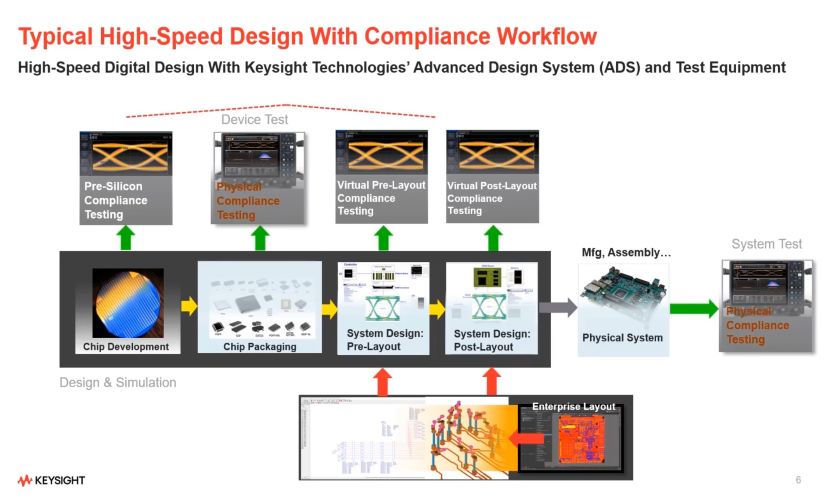

Faster networking speeds require faster memory. Each new version of the DDR standards supports more rapid access to data stored in memory. As data speeds reach 6.4 GT/s with DDR5, you face new design and validation challenges. Design and simulation of DDR5 memory systems help you discover issues before silicon tape-out and ensure good signal integrity of your designs. Design and simulation software enables you to optimize your transmitter, receiver, and channel designs for the best performance and reliability at the desired speed. We can help you design upfront to resolve signal integrity issues, ensure power efficiency, and stay within tight error margins before prototyping.

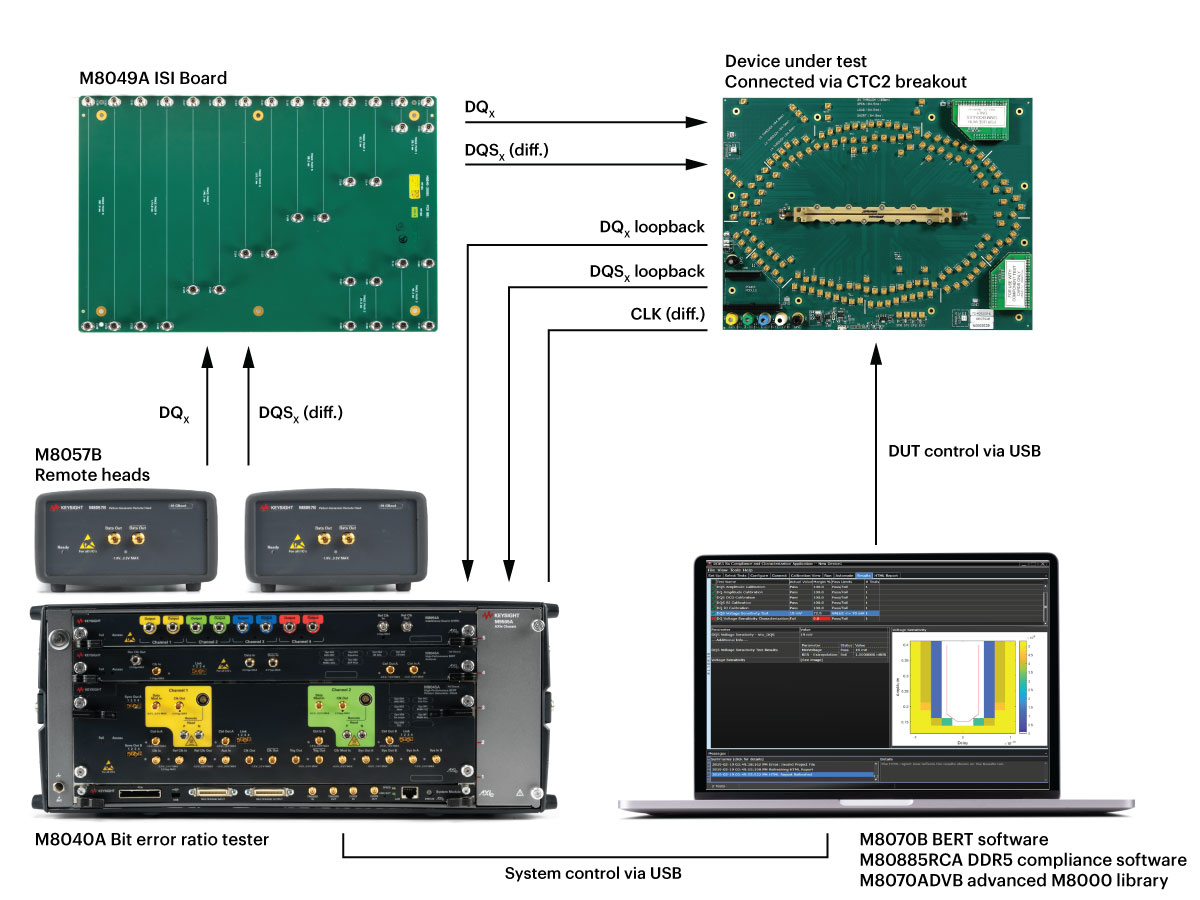

Ensuring interoperability of your DDR5 transmitter with other devices requires you to test it against JEDEC conformance standards. When testing your DDR5 devices, automate the calibration, setup, execution, and documentation of your compliance tests with purpose-built hardware and software. Ideally, use a high-bandwidth oscilloscope (25 GHz+) with a high effective number of bits, high-bandwidth probes designed for minimal effects on the measured signal, and interposer boards for probing as close to the silicon as possible. Couple this with software for test configuration, execution, evaluation, automation, and report generation.

Ensuring compliance with the fifth generation of double data rate memory (DDR5) devices requires the performance of an exhaustive list of interoperability tests set forth by the JEDEC specifications. Physical layer receiver conformance testing involves characterization of the receiver, calibration of a stress signal using a high-bandwidth oscilloscope, and device receiver tests with a bit error ratio tester.

Data corruption is a common symptom encountered during the validation of DDR5 designs. The root cause of data corruption can be difficult to determine. Usually, there are either signal integrity or functional issues with your designs.

When DDR5 memory systems do not behave as expected, you need functional debug, analysis, and protocol compliance validation solutions that provide trace capture and analysis capabilities. We can offer you the necessary insight to understand your system’s behavior and quickly find the root cause of any issues.

LPDDR Design-to-Test Solutions

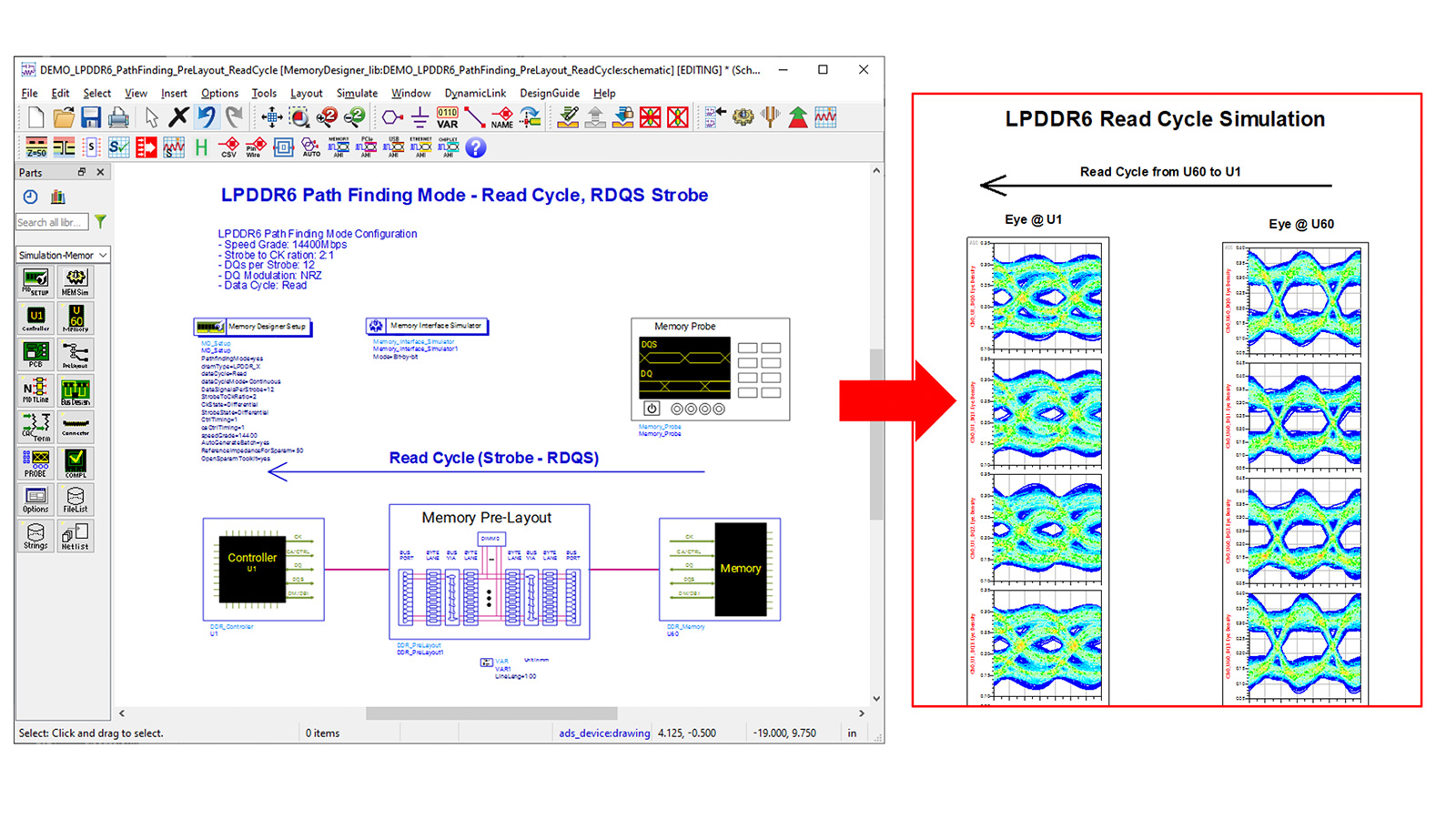

Given the low power consumption requirements for mobile devices, LPDDR designs require higher power efficiency. With simulation, you can detect problems in your lower-voltage LPDDR designs before prototyping. Design with Keysight PathWave software and gain insights into voltage management and signal integrity, ensuring precise timing and minimal crosstalk at higher speeds. Advanced IBIS-AMI models account for the complexity of LPDDR configurations to ensure robust performance and reliability of your design.

LPDDR6 technology enables higher bandwidth for data transfer with lower power. An oscilloscope with sufficient bandwidth and the highest signal integrity is mandatory for transmitter testing. To guarantee compliance with the JEDEC standard and minimize test time, Keysight offers the most comprehensive test automation applications that work hand in hand with Keysight's highest-speed test instruments.

Testing LPDDR6 receivers poses significant challenges due to the high-speed data transfer rates, which narrow the margins and make the design work and testing more intricate. Automated test tools like bit error rate testers (BERTs), oscilloscopes, and compliance software are essential to address these challenges at the physical layer, ensuring minimum test time, accurate measurements, and compliance with the JEDEC specifications.

Interoperability testing is also mandatory on the protocol level while data LPDDR data speeds are rising. To ensure data integrity, you must focus on timing and event monitoring to capture and analyze signals accurately. Additionally, evaluating performance improvement from training and refresh management ensures the system operates reliably and efficiently. Keysight offers solutions tailored for fast and reliable LPDDR protocol analysis for your design.

Resources

Want help or have questions?