무엇을 찾고 있습니까?

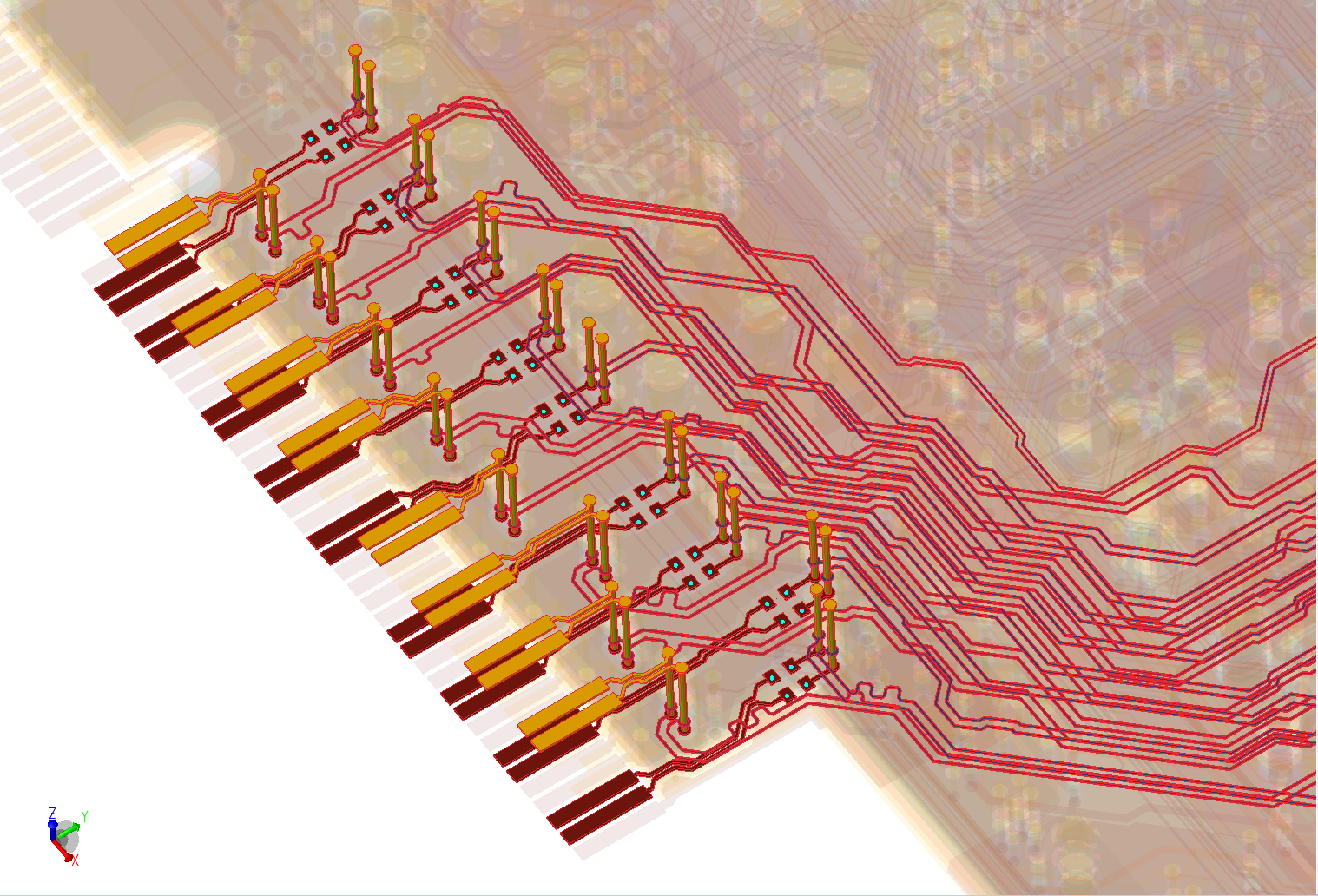

오늘날의 더 조밀하고 복잡한 디자인을 처리하려면 설계자에게 민첩한 작업이 요구됩니다. 키사이트 EDA의 ADS(Advanced Design System)는 협업 가이드 및 표준 기반 워크플로우를 통해 설계 검증 및 규정 준수를 간소화합니다.

표준 중심 워크플로우

DDR 5/6 모델 추출, 신호 무결성 및 규정 준수 확인

ADS 메모리 설계자들은 수신기를 위한 IBIS-AMI 모델을 생성하고, DDR 채널의 정확한 전자기(EM) 모델을 추출하고, 특정 비트 오류율에서 아이 마스크에 대한 마진을 예측해야 합니다.

최신 메모리 표준인 DDR5 및 GDDR6에 대한 기본 지원과 정확성을 갖춘 고급 신호 무결성 분석 기능을 통해 설계자는 이전보다 5배 빠르게 종합적인 DDR 분석을 설정할 수 있습니다.

Chiplet die-to-die link 신호 무결성 및 규정 준수 검증

ADS Chiplet PHY Designer를 사용하면 설계자는 Chiplet의 다이 간 상호 연결에 대한 VTF와 같은 종단 간 링크 마진 및 규정 준수 측정을 예측할 수 있습니다.

이를 통해 UCIe에서 전달된 클럭킹을 정확하게 분석하여 지터 추적을 고려할 수 있습니다. 표준별 측정에 대한 지원이 내장되어 있어 알려진 Chiplet 표준 준수 여부를 쉽게 확인할 수 있습니다.

"PCIe® 5/6 신호 무결성 및 가상 컴플라이언스 테스트

ADS PCIe Designer는 스마트 설계 환경을 사용하여 다중 링크, 다중 레인 및 다중 레벨(PAM4) PCIe 시스템 설정을 자동화합니다. NRZ 및 PAM4 변조를 지원하는 PCIe AMI 모델러는 PCIe 시스템의 빠른 구현을 촉진합니다.

통합된 시뮬레이션 기반 적합성(Compliance) 테스트 솔루션은 설계 반복을 최소화하고 출시 기간을 단축하여 설계 비용을 절감할 수 있습니다.

고속 시리얼의 신호 무결성

디지털 표준이 새롭게 등장할 때마다 속도가 더 빨라지고 주파수가 더 커지게 됩니다. 신호 무결성 엔지니어는 크로스톡, 신호 손실, 지터 및 이퀄라이제이션을 관리하면서 최적의 비아 설계를 포함해 채널 설계에 대한 자신감을 가져야 합니다.

ADS의 고급 채널 에뮬레이션을 사용하면 펄스형 진폭 변조(PAM-4, PAM-3, PAM-N) 시그널링 구조에 대한 시뮬레이션이 가능합니다. 또한 빠르고 정확한 신호 무결성 EM 분석으로 구축 전에 중요한 오류를 포착할 수 있어 보드 설계 성공률 100%를 달성할 수 있습니다.

View Lessons

Designing for Signal Integrity (10 min)

전력 무결성: More Than Just DC

전압이 더 낮고, 전류가 더 높고, 공급장치가 다양한 상황에서는 전력 무결성 문제를 해결하기가 까다로울 수 있으며 수정하는 데 막대한 비용이 초래됩니다. 이 과제를 극복하려면 배전망(PDN)의 주파수 및 시간 도메인 분석을 위한 효과적으로 통합되고 조화를 이루는 설계 흐름이 필요합니다.

키사이트의 PI 설계 워크플로를 사용하면 동적 부하에 의해 발생하는 최악의 리플을 시각화하고 최적의 저노이즈 PDN을 엔지니어링할 수 있습니다.

다중물리(Multi-Physics) 시뮬레이션

복잡한 형상, 다양한 재료 및 고주파수를 갖춘 밀도가 높은 전자 장치에는 더욱 발전된 EM 시뮬레이션이 필요합니다.

유한요소법(FEM)은 불규칙한 모양을 처리하고, 재료 특성을 통합하고, 다중 물리(열 또는 전자기) 분석을 가능하게 하여 이러한 복잡성을 해결합니다. 이는 장치 성능에 대한 전체적인 관점을 제공하여 물리적 프로토타입 제작 위험을 줄입니다.

고속 디지털 설계: Go Deeper

인쇄 회로 기판(PCB)은 기술이 발전하고 장치가 축소됨에 따라 더욱 복잡해지고 밀도가 높아졌습니다.

전문가를 위해 엄선된 주제들을 통해 표준 기반 워크플로, 신호 및 전력 무결성에 대해 자세히 알아보십시오.

혁신적인 테스트 자산 보호

전자 설계 및 고속 디지털 설계 FAQ

전자 설계, 고속디지털 설계, 표준기반 설계에 대한 일반적인 질문과 답변을 안내합니다.

전자 설계는 전자 회로 및 시스템을 생성, 테스트 및 최적화하는 프로세스입니다. 여기에는 아날로그, 디지털 또는 혼합 신호 구성 요소와 기술이 포함될 수 있으며 통신, 데이터 센터, 반도체 등 다양한 영역에 적용됩니다.

EDA 소프트웨어는 전자 회로 및 시스템용 도구의 컴퓨터 지원 설계 범주입니다. EDA 소프트웨어 도구는 제조 또는 구현 전에 다양한 조건과 시나리오에서 전자 회로 및 시스템의 동작과 성능을 시뮬레이션합니다. 논리, 기능, 타이밍, 전기, 열, 전자기 등 다양한 유형의 시뮬레이션을 수행하여 설계자가 설계 오류의 위험을 줄이고 최종 제품의 품질을 개선하며 개발 프로세스에서 시간과 비용을 절약할 수 있도록 돕습니다.

고속 디지털 설계는 높은 데이터 속도로 작동하는 디지털 회로 및 통신 시스템의 물리적 계층을 다루는 전자 설계의 하위 집합입니다. 신호 무결성, 전력 무결성, 전자기 간섭 및 열 관리의 영향에 특별한 주의가 필요합니다. 고속 디지털 설계를 통해 전자 시스템에서 더 빠른 데이터 전송, 더 낮은 전력 소비 및 더 높은 성능을 구현할 수 있습니다.

표준 기반 설계는 서로 다른 장치와 시스템 간의 통신, 데이터 교환 및 상호 운용성을 위해 미리 정의된 사양과 프로토콜을 따르는 전자 설계 방법입니다. 표준 기반 설계는 전자 시스템의 호환성, 신뢰성 및 확장성을 촉진할 수 있습니다. 표준 기반 설계의 예로는 USB, PCIe®, UCIe 및 DDR이 있습니다.

USB는 컴퓨터, 스마트폰, 카메라, 주변기기 등 장치와 호스트 간의 통신 및 전원 공급을 위한 표준입니다. USB는 1.5Mbps(USB 1.0)부터 80Gbps(USB4 버전 2.0)까지 다양한 데이터 속도를 지원합니다. USB는 또한 2.5W(USB 2.0)부터 240W(USB PD 3.1)까지 다양한 전력 공급 모드를 지원합니다. USB4 버전 2.0은 표준의 최신 버전이며 USB 3.2, USB 2.0 및 Thunderbolt 3과 역호환됩니다.

PCIe는 컴퓨터, 그래픽 카드, 네트워크 카드, 저장 장치 등 장치와 호스트 간의 고속 직렬 통신을 위한 표준입니다. PCIe는 2.5GT/s(PCIe 1.0)부터 64GT/s(PCIe 6.0)까지 다양한 데이터 속도를 지원합니다. PCI-SIG®(PCI Special Interest Group)는 PCIe 시스템의 상호 운용성을 보장하는 사양 및 규정 준수 테스트를 정의합니다. 또한 PCIe는 x1에서 x32까지 다양한 레인 구성을 지원하여 대역폭과 성능을 향상시킵니다.

UCIe(Universal Chiplet Interconnect Express)는 Chiplet 간의 고속 직렬 통신을 위한 표준입니다. 설계자는 이러한 소형 집적 회로를 결합하여 더 크고 복잡한 칩을 형성할 수 있습니다. UCIe는 CXL/PCIe를 기반으로 하며 동일한 데이터 속도와 레인 구성을 지원합니다. UCIe는 비용, 전력 소비 및 설계 복잡성을 줄이는 동시에 성능과 확장성을 높이는 Chiplet 기반 설계를 가능하게 합니다.

DDR(Double Data Rate) SDRAM은 컴퓨터, 메모리 모듈, 그래픽 카드 등 장치와 호스트 간의 고속 메모리 통신을 위한 표준입니다. DDR은 200Mbps(DDR)부터 6400Mbps(DDR5)까지 다양한 데이터 속도를 지원합니다. DDR은 또한 64MB(DDR)부터 64GB(DDR5)까지 다양한 메모리 용량을 지원합니다. DDR은 클록 신호의 상승 및 하강 에지에서 데이터를 전송하여 유효 대역폭을 두 배로 늘립니다.

Chiplet은 특정 기능을 매우 잘 수행하는 소형 모듈식 칩입니다. 예를 들어, Chiplet은 프로세서 코어, 메모리 블록, I/O 드라이버 또는 신호 처리 장치가 될 수 있습니다. Chiplet은 UCIe와 같은 표준화된 고속 디지털 인터페이스를 통해 여러 개의 Chiplet이 연결되어 완전한 시스템 온 칩(SoC)을 형성하는 Chiplet 기반 아키텍처에서 사용되도록 설계되었습니다.

다른 도움이 필요하십니까?