B4661A Memory Analysis Software for Logic Analyzers

Data Sheets

B4661A Memory Analysis Software for Logic Analyzers

Overview

The Keysight B4661A memory analysis software offers a suite of viewers and tools that include a protocol compliance violation testing capability across speed changes, a condensed traffic overview for rapid navigation to areas of interest in the logic analyzer trace, powerful performance analysis graphics, and DDR and LPDDR decoders. With the B4661A memory analysis software and a Keysight logic analyzer, users can monitor DDR3/4/5 or LPDDR2/3/4/5 systems to debug, improve performance, and validate protocol compliance. Powerful traffic overviews, multiple viewing choices, and real-time compliance violation triggering help identify elusive DDR/LPDDR system violations.

The Keysight B4661A memory analysis software provides four standard software features and seven licensed memory analysis options. GDDR6 analysis (B4661A-7FP/7TP/7NP) will be added in the 6.60 release in January 2020.

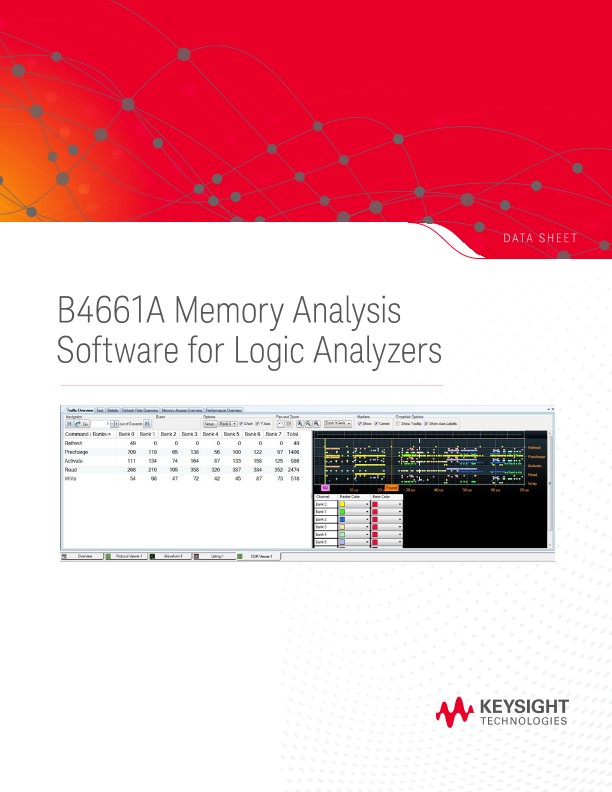

Traffic Overview

Command graphing

Using traffic overview, each command on the bus is a row in the table. Columns vary depending on the viewing option chosen. Users choose from the following viewing options:

–View all ranks – in this mode, the table columns are “All ranks,” “Rank 0,” Rank 1,” etc. The chart shows a different color dot on a different line for each rank.

–View a single rank – The table columns are “All banks,” “Bank 0,” etc. (For DDR4, the columns are “All BG/BA”, then all combinations of BG and BA.) The chart shows one line of dots. A choice for which bank to view in the chart is enabled.

–All banks – The chart shows a dot for every command on the rank, regardless of bank. All dots are the same color.

–A single bank – The chart shows a dot for commands that apply only to the selected bank.

–If the user has a multi-rank system and wants to see charts of each rank simultaneously, then they can use multiple applications of the tool.

Details Tab

For LPDDR2/3/4/5, DDR3/4/5, and GDDR6, this tab displays the details of a selected memory transaction and all other transactions in the same sequence or ‘open/closed page’. ‘Pages’ open with Activate commands, all Reads or Writes associated with the same Rank, Bank Group, Bank, and Row Address are part of the ‘open page’. Pages close with an associated Precharge. When either a Read or Write transaction is selected, the Data associated with the selected Read or Write is also displayed with the associated address.

For ONFi, this tab displays the details of an ONFi transaction selected in the upper pane. You can also visualize an ONFi operation as a set of logically grouped commands in a sequence in the details tab.

LPDDR5 Analysis and Compliance Validation (B4661A-6FP/6TP/6NP)

Achieve greater insight faster using the B4661 memory analysis and compliance validation licensed software for LPDDR5 memory. LPDDR testing, protocol compliance and debug work has become more complex and time consuming over the years as data rates increase and the memory architectures become more complex. Using the LPDDR5 analysis and protocol compliance validation, navigation to problem areas is simplified with a powerful traffic overview that presents the LPDDR5 traffic from the logic analyzer trace capture at the protocol level with user-selected filtering.

Licensed option B4661A-6FP/6TP/6NP consists of a LPDDR5 analysis viewer with multiple tabs/views and two LPDDR5 protocol compliance tools, a Real-time DDR5 protocol compliance tool and a Post-process LPDDR5 protocol compliance tool.

Real-time LPDDR5 protocol compliance analysis

The automated real-time compliance analysis tool detects and captures state machine, protocol compliance, and protocol level bus cycle timing violations for LPDDR5. Real-time violation detection is an important advancement in DDR memory debug and valida¬tion. Monitoring your LPDDR5 bus real-time means the Keysight logic analyzer will continuously monitor the bus for the selected test and trigger if it occurs within the specified time.

LPDDR5 Real-time testing enables

Monitoring for compliance violations while running specific routines on the system under test. Unique feature of real-time compliance tool allows custom regression test suites to be created from a valid logic analyzer trigger for any valid Keysight logic analyzer configuration compatible with the B4661A.

The real-time compliance violation analysis tool cycles through preset or user-edited parameters for a selectable time limit on each parameter to capture logic analyzer traces of the DDR5 bus, triggering on the violation. The tool allows the user to save multiple traces of violations and produces a summary report when complete.

Real-time compliance analysis

The automated real-time compliance analysis tool detects and captures state machine, protocol compliance, and protocol level bus cycle timing violations for DDR3/4 or LPDDR2/3/4. Real-time violation detection is an important advancement in DDR memory debug and validation. Monitoring your DDR bus real-time means the Keysight logic analyzer will continuously monitor the bus for the selected test and trigger if it occurs within the specified time frame. Beyond monitoring your DDR3/4 or LPDDR2/3/4 system real-time for elusive violations, designers can also monitor other digital system continuously for elusive, intermittent violations in protocol compliance or bus level timing.

Physical address conversion tool in both DDR3/4 and LPDDR2/3 decoders with integrated trigger creation

Setting up a trigger on a specific physical address to obtain the corresponding data bus can be very tedious. The physical address trigger tool is included in the B4661A DDR decoder and LPDDR decoder options. The trigger tool allows you to automatically create a trigger on a specific physical address without having to go through a step-by-step trigger add-in. The physical address trigger tool incorporates a user-friendly interface to help the user quickly setup the trigger. DDR2/3/4 and LPDDR2/3 are covered by the physical address trigger tool. LPDDR4 is not covered by the physical address trigger tool.