How to Test and Debug DDR4 Memory Systems

Performing DDR4 functional validation and protocol debug

Implementing a double data rate 4 (DDR4) memory system requires engineers to perform thorough read / write functional tests. They require a solution that can quickly step through, isolate, and uncover issues, such as memory write-back, initialization, system crashes, and system abnormalities. To perform a complete protocol validation and performance improvement of DDR4 systems, test engineers need a logic analyzer that can stream bus signals and record them at specific data rates.

Special DDR4 dual in-line memory module (DIMM) or ball grid array (BGA) hardware interposers are required to capture the complete bus trace signals reliably. Memory analysis software is critical to analyze the performance and functional protocol compliance, including post-process compliance violations across speed changes. Engineers should also monitor memory performance with qualitative insights for hundreds of signals and bus-level signal integrity.

DDR4 test and debug solution

Explore products to test and debug DDR4 memory systems

-

![M9505A AXIe 5-Slot Chassis]()

M9505A AXIe 5-Slot Chassis

-

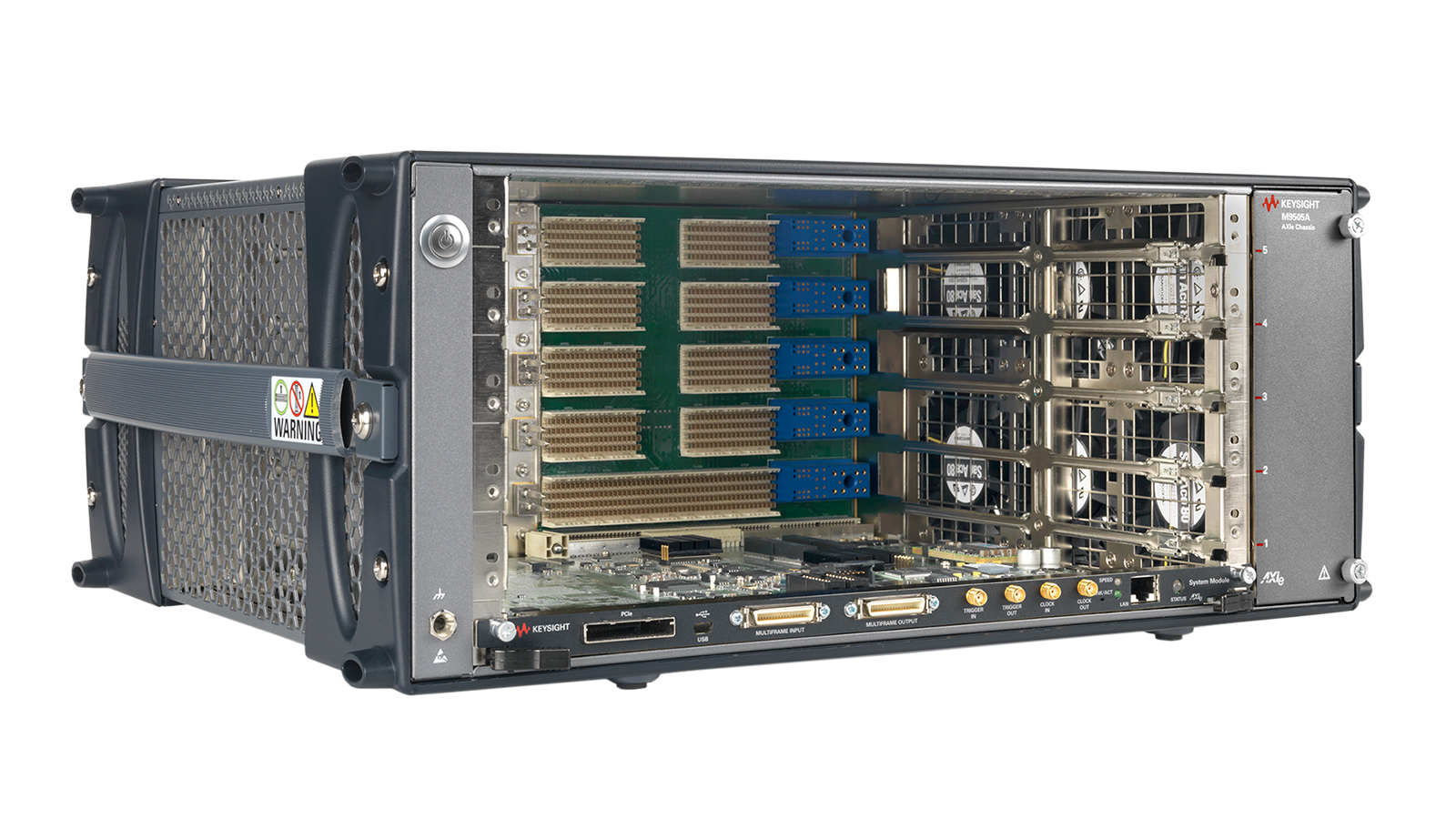

![W4643A DDR4 x4/x8 BGA Interposer for Logic Analyzer, Connects to 61-pin ZIF]()

W4643A DDR4 x4/x8 BGA Interposer for Logic Analyzer, Connects to 61-pin ZIF

-

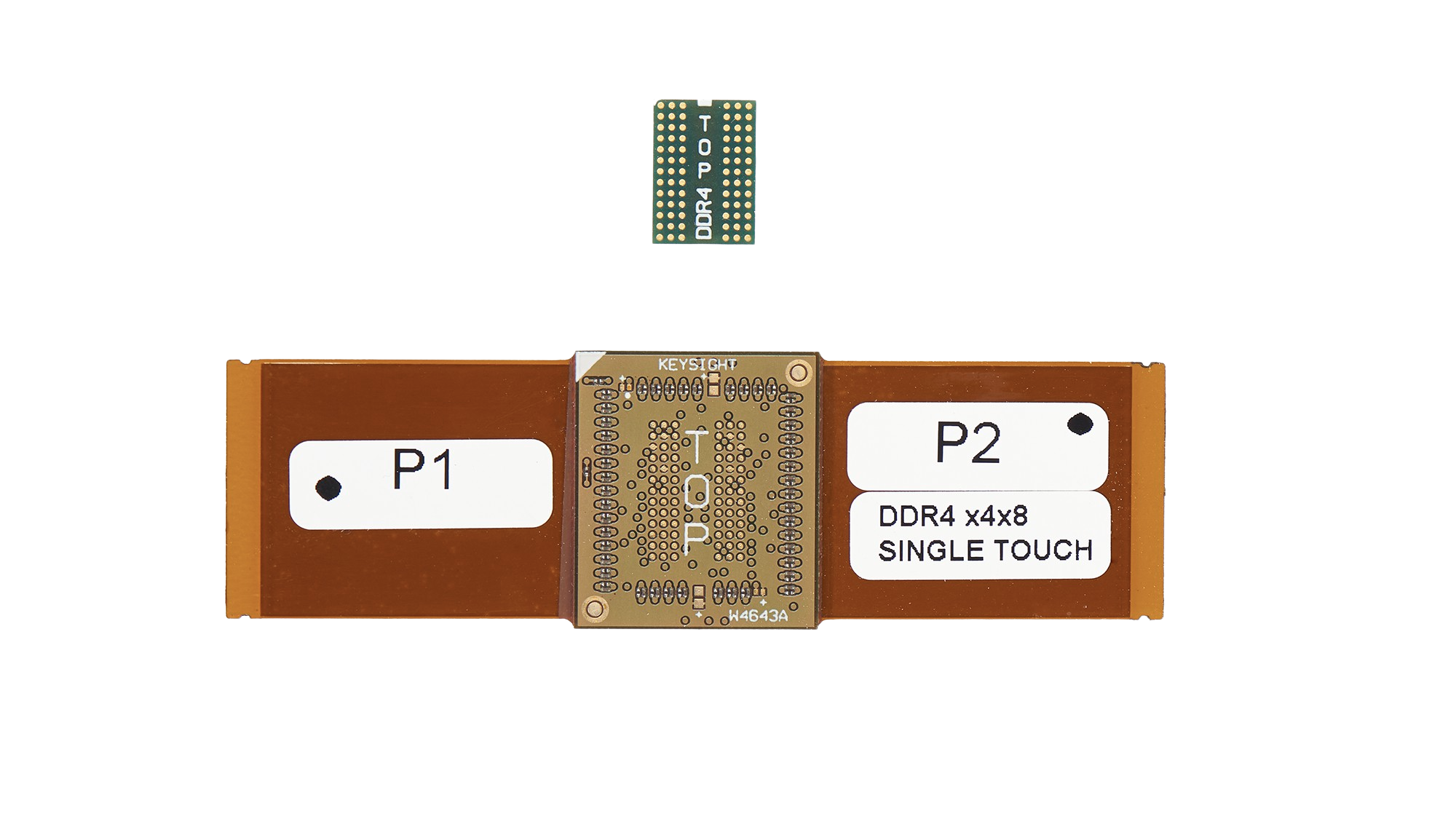

![U4164A Logic Analyzer Module with State Mode up to 4Gb/s]()

U4164A Logic Analyzer Module with State Mode up to 4Gb/s

-

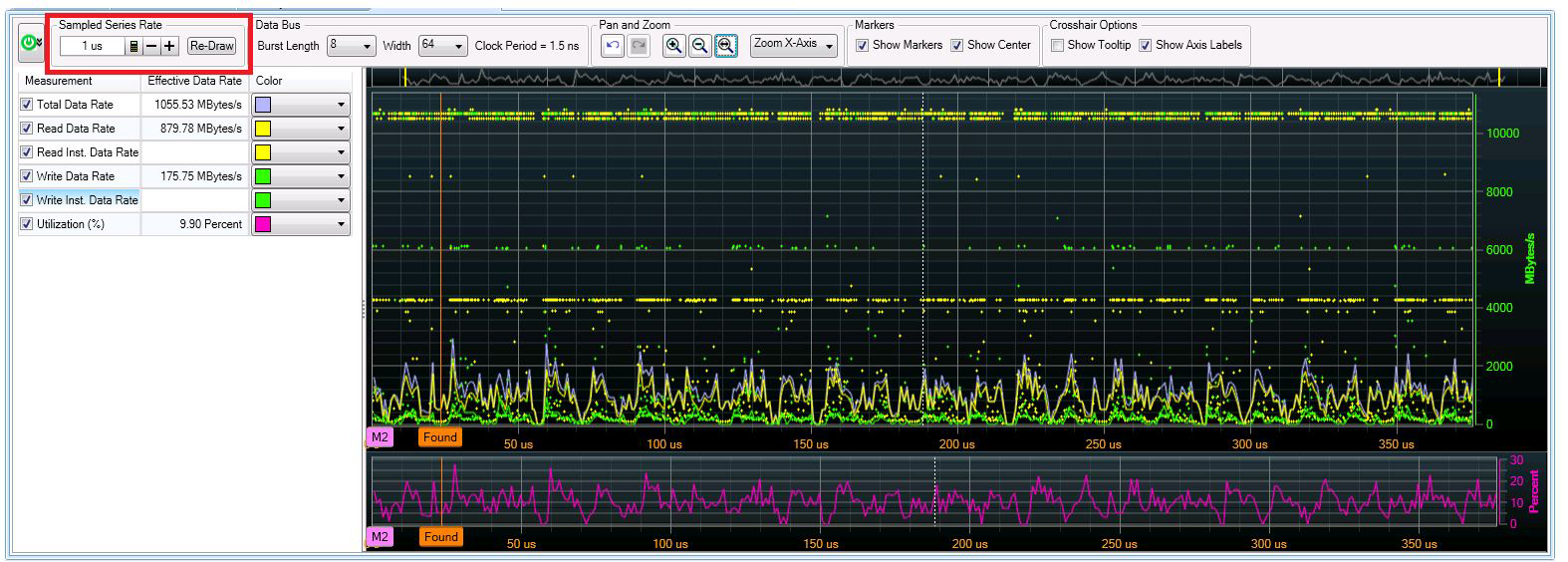

![B4661A Memory Analysis Software for Logic Analyzers]()

B4661A Memory Analysis Software for Logic Analyzers

How to Test and Debug DDR4 Systems

M9505A AXIe 5-Slot Chassis

M9505A 5-slot AXIe chassis with embedded system module and Gen 2, x8 link to external controller

Specs

| Description | M9505A 5-slot AXIe chassis with embedded system module and Gen 2, x8 link to external controller. |

| Slots | 5 slots |

| Form Factor |

|

| Height |

|

| Slots | 5 slots |

| Bandwidth | 4 GB/s |

| Connectivity |

|

| Type |

|

| Platform |

|

| Height |

|

How to Test and Debug DDR4 Systems

W4643A DDR4 x4/x8 BGA Interposer for Logic Analyzer, Connects to 61-pin ZIF

The W4643A DDR4 x4/x8 - 2 wing BGA interposer for 78-ball DDR4 DRAM. It is designed for data rates up to and including 3.3 Gb/s. It captures all ADD/CMD/DQ/DQS.

Specs

| Connector Type |

|

| Applications |

|

How to Test and Debug DDR4 Systems

U4164A Logic Analyzer Module with State Mode up to 4Gb/s

The U4164A logic analyzer provides industry’s highest data rate state mode (up to 4 Gb/s), highest deep trace timing mode (up to 10 GHz), and deepest memory (up to 400 Mb), enabling validation and debug of DDR4 or LPDDR4 at data rates over 3.5 Gb/s.

Specs

| Includes Pattern Generation (Stimulus) | |

| Max Timing Speed | |

| Number of channels |

|

| Max memory depth | 400 Mpts |

| Signal Type |

How to Test and Debug DDR4 Systems

B4661A Memory Analysis Software for Logic Analyzers

Achieve greater insight faster using the B4661A memory analysis software and your Keysight logic analyzer system for debug and validation of DDR3, DDR4, DDR5, LPDDR2, LPDDR3, LPDDR4, or LPDDR5 systems.

Specs

| Includes Pattern Generation (Stimulus) | |

| Max Timing Speed | |

| Number of channels | |

| Max memory depth | |

| Signal Type |

Discover resources and insights

Additional resources for testing and debugging DDR4 memory systems

-

White paper

Learn How to Overcome DDR Memory Test Challenges From DDR3 to DDR5

-

Configuration guide

Tailor the DDR4 Reference Solution System to Meet Your Requirements

-

Datasheet

Explore the U4164A Logic Analyzer Module

-

Datasheet

Explore B4661A Memory Analysis Software for Logic Analyzers

Related use cases

-

![How to Analyze PAM4 Receiver Signals]() segmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs

segmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGssegmentation:campaign/Digital_High_Performance,segmentation:business-unit/CSG,keysight:product-lines/24,segmentation:funnel/mofu,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGsHow to Analyze PAM4 Receiver Signals

Analyzing PAM4 signals requires multiple-bit error rate (BER) and symbol error rate (SER) measurements. Learn how to characterize a PAM4 signal at the receiver fully.

Learn more

-

![How to Test PCIe® 5.0 Receiver Compliance]() segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/software

segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwareHow to Test PCIe® 5.0 Receiver Compliance

Verifying Peripheral Component Interconnect Express (PCIe) receiver compliance involves testing the PCIe® 5.0 device's receiver performance with a bit error ratio tester. Learn how to calibrate your stress signal and test for PCIe 5.0 receiver compliance with automated test tools.

Learn more

-

![How to Test PCIe® 6.0 Receiver Compliance]() segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/software

segmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwaresegmentation:business-unit/CSG,segmentation:campaign/Digital_High_Performance,segmentation:product-category/Test_Automation_Software,segmentation:product-category/Test_Automation_Software/SW_Oscilloscopes_BERTs_AWGs,segmentation:funnel/mofu,keysight:product-lines/24,keysight:dtx/solutions/facets/development-area/high-speed-digital,keysight:dtx/solutions/facets/design-and-test-product/bit-error-ratio-testers,keysight:dtx/solutions/facets/workflow-stage/conformance-and-compliance,keysight:dtx/solutions/facets/industry/wireline-communications,segmentation:search-relevance-product/softwareHow to Test PCIe® 6.0 Receiver Compliance

Testing PCI-SIG devices requires robust receiver compliance validation to certify PCIe® 6.0 device interoperability at 64 GT/s with PAM4 signals. Learn how to calibrate your stress signal and test for PCIe 5.0 receiver compliance with automated test tools.

Learn more

Get in touch with one of our experts

Need help finding the right solution for you?